搭建验证平台也并不是一件容易的事情。同时由于不同验证工程师搭建的风格不太一致,所以在一个项目中常会出现不好管理,甚至前后不一相互矛盾的

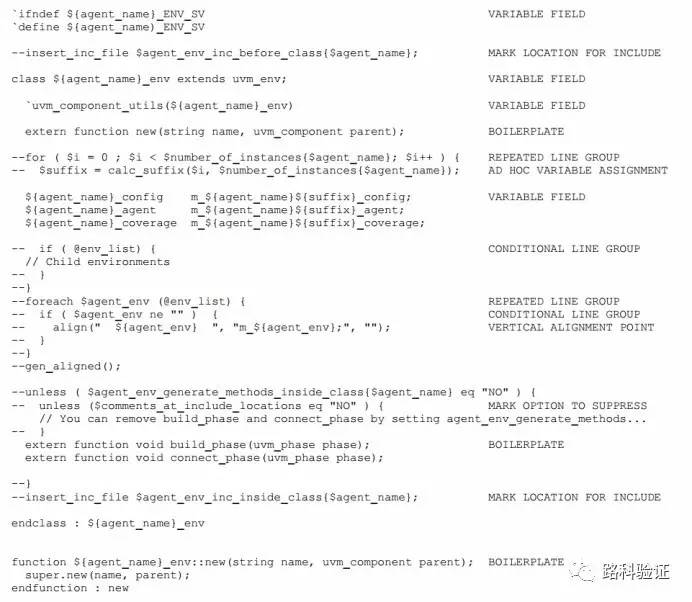

每个UVM测试平台代码库可以分为两部分,封装好且基本保持不变的样板代码部分和需要用户自定义的代码部分。基于此,就要求我们所生成的代码能够包含相当多的用户自定义元素。理论上,我们生成代码的基本原则是,先调用UVM,定义好一些结构语法都正确的SystemVerilog模板代码,然后我们基于此进行复制和配置得到我们的代码。这就要求我们的模板代码至少要能包含以下几个元素:

我们使用这些变量元素表明,我们期待自动生成的UVM代码是具有一定灵活性的,不能仅仅简单复制一段源文件来实现。我们希望以脚本来实现UVM代码生成器的功能。这个代码生成器会生成一系列的class、package、module、和intece。

如上所述,使用一些配置文件对变量、对代码进行约束,然后基于模板代码生成目标代码,这一方法能够使得代码具备一定的灵活性。除了用户定义的代码片段可能会引入的错误之外,我们原本生成的生成的代码应该是完整的,可以使用生成的仿真脚本运行操作。

当然,本文的目的不是你使用这个特定的代码生成器,而是让你更好地了解UVM代码生成的基本内在步骤。

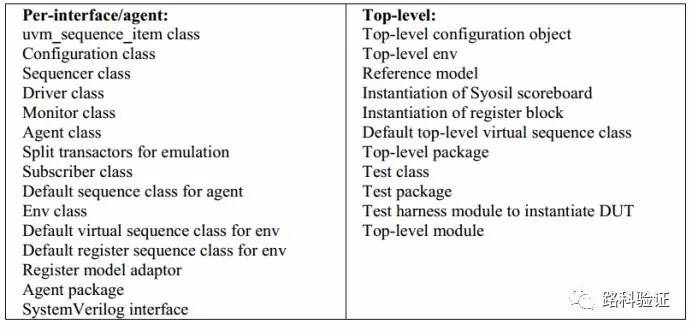

代码生成器在实现特定的代码时,要考虑哪些要求呢?如前所述,每个工程师的代码风格都不尽相同,当在文件级别考虑实现我们的代码生成器时,以下这些问题我们就一定要注意到了:

本文中的要点不是为了在UVM对testbanch的生成方法中作出具体的选择,只是给出参考,选择任何类似可行的的结构都是有效的。

在更详细的层面上,简单的UVM代码生成器就需要对UVM的具体feature进行选择了,如下:

从顶层模块通过配置数据库传递virtual intece到agent要选择哪种机制呢?

上述都是只代表了常规的编码选择,除此之外,代码生成器还要求对另外一些文件的自动化生成,这些文件手写起来是相当费时的。

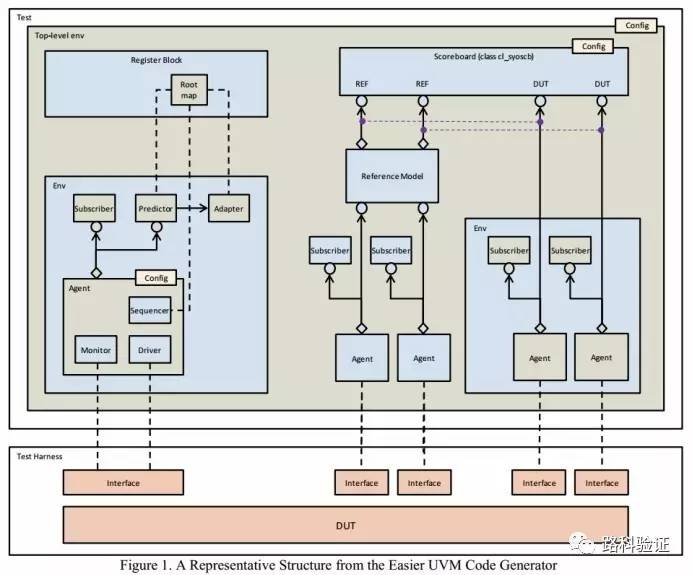

上图显示了一个简单UVM代码生成器能够产生的结构类型的示例,包括多个DUT接口和相关agent,嵌套envs以及寄存器块,参考模型和记分板的实例化。 请注意,代码生成器不会生成寄存器模型,参考模型或记分板的内容。 寄存器模型通常来自单独的生成器,现在可有许多文章对此进行讨论。参考模型则是必须要手动编码的。

对于新用户:代码生成器可以迅速生成有效的代码示例模板。对于新手搭建和理解的好处是巨大的。

对于所有用户:提高了生产效率,避免了搭建中出现的繁琐的重复和容易出错的工作。保持了代码风格的一致性,自动生成的代码风格一定是统一的,避免了因代码风格问题导致的意外,使测试平台代码更易读、易。

对UVM代码生成器的功能是没有上限的,应该实现多复杂的功能,取决于你们的需要和付出回报比。代码生成器总是要不断向前发展的,以改进编码风格和处理新的问题,同时该进的时候还要注意要能能向后兼容配置文件,随时可以重新生成整个代码库。

谢谢你对科验证的关注,也欢迎你分享和转发真正的技术价值,你的支持是我们保持前行的动力。返回搜狐,查看更多

推荐:

网友评论 ()条 查看